直列入力並列出力(SIPO)

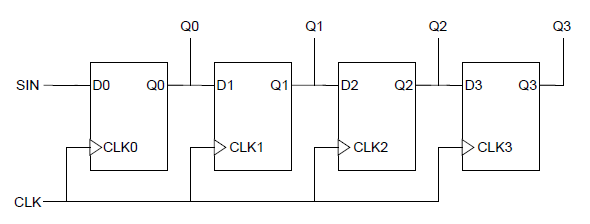

直列入力並列出力(SIPO: Serial-in Parallel-out)のシフトレジスターについて。複数のDフリップフロップを出力と入力で数珠つなぎにするとSIPOのシフトレジスターを構成できる。

以下は4ビットのシフトレジスターの簡単な例。

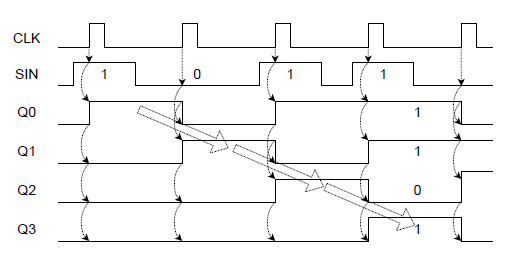

タイミングチャートで表すと、以下の様にCLKの立ち上がりのたびにSIN→Q0、Q0→Q1、Q1→Q2、Q2→Q3と1ビットの値がシフトしていく。

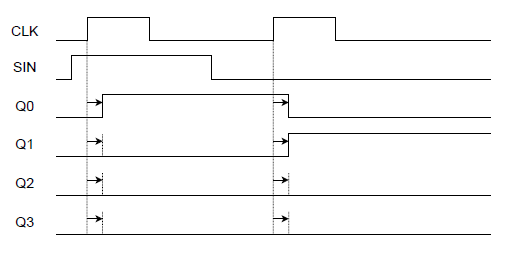

ここで、CLKの立ち上がり時にSIN→Q0→Q1→Q2→Q3と一斉に値が反映されてしまわないかということが気になる。

以下はクロックパルスの部分を誇張して描いたタイミングチャート。ここで、各Dフリップフロップに入力が与えられてから、それが出力に反映されるまで、僅かな時間だが遅延があることを表現している。

このため、CLKの立ち上がりが各Dフリップフロップに一斉に届いたとしても、SINの信号が使われるのはQ0のみになることがわかる。

実際のシフトレジスターには、内容をクリアする端子や、パラレル信号を取り出すための端子などが備えられている。